デマルチプレクサは、入力信号を指定された出力端子から出力する回路です。マルチプレクサの逆の機能を持ちます。

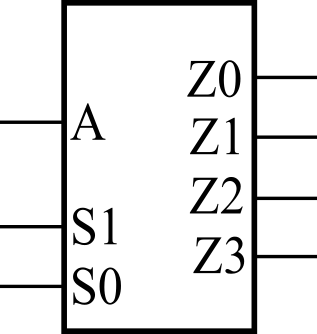

図1は、1ビット入力信号AをS0とS1の値に応じでZ0~Z3端子から出力するデマルチプレクサのシンボル図です。表1は、図1のデマルチプレクサの真理値表です。S0=0,S1=0のときAをZ0から出力し、S0=1,S1=0のときAをZ1から出力し、S0=0,S1=1のときAをZ2から出力し、S0=1,S1=1のときAをZ3から出力します。

| 入力 | 出力 | |||||

|---|---|---|---|---|---|---|

| A | S1 | S0 | Z0 | Z1 | Z2 | Z3 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 |

表1の出力Z0~Z3は、A=0のときはS0, S1の値とは無関係にすべて0です。よって、ドントケアを使うと表2のように簡単になります。

| 入力 | 出力 | |||||

|---|---|---|---|---|---|---|

| A | S1 | S0 | Z0 | Z1 | Z2 | Z3 |

| 0 | x | x | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 |

デマルチプレクサの論理式

出力Z0~Z3について表2から主加法標準形で論理式を作成します。出力Z0~Z3が1になるA, S0, S1の組み合わせはそれぞれ1ヵ所なので、図1の内部を構成する論理式は式(1)~(4)のようになります。

$$Z0 = A \cdot \overline{S1 }\ \cdot \overline{S0}\ \ \ \ \ \text{(1)}$$ $$Z1 = A \cdot \overline{S1 } \cdot S0\ \ \ \ \ \text{(2)}$$ $$Z2 = A \cdot S1 \cdot \overline{S0}\ \ \ \ \ \text{(3)}$$ $$Z3 = A \cdot S1 \cdot S0\ \ \ \ \ \text{(4)}$$

HDL記述

図1のマルチプレクサをVerilogで記述したのがリスト1です。(1)~(4)の論理式とほとんど同じ記述になります。

リスト1