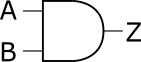

ANDゲートは、すべての入力端子に入力された値が1の時だけ、出力端子から1の値を出力する基本ゲートです。一番シンプルなANDゲートは、入力端子数が2のANDゲートです(図1)。2入力ANDゲートのシンボルは、2つの入力端子と1つの出力端子を持ちます。

2入力ANDゲートを論理式で表したのが、(1)です。

$$Z = A \cdot B \ \ \ \ \ \text{(1)}$$

2入力ANDゲートの真理値表は、\(2^2=4\)で4通りの入力の組み合わせがあります(表1)。2入力ANDゲートは、入力端子Aと入力端子Bの両方が1の時だけ出力端子Zが1になり、それ以外の場合は出力端子Zが0になります。

| 入力 | 出力 | |

|---|---|---|

| A | B | Z |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

リスト1は、ハードウェア記述言語(HDL)のVerilogで記述した2入力ANDゲートです。

リスト1

module and2_mod (

input A,

input B,

output Z

);

assign Z = A & B;

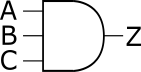

endmoduleANDゲートは、3,4,5…といったように、2つ以上の入力端子を持つ種類もあります。3入力ANDゲートのシンボルは、3つの入力端子と1つの出力端子を持ちます(図2)。3入力ANDゲートの論理式が(2)です。論理式からわかるように、3入力ANDゲートは、2つの2入力ANDゲートで実現できます。

$$Z = A \cdot B \cdot C \ \ \ \ \ \text{(2)}$$

3入力ANDゲートは、入力端子が3本なので、真理値表は\(2^3=8\)の8通りの組み合わせがあります(表2)。3入力ANDゲートは、すべての入力端子の値が1の時だけ、出力端子Zが1になります。ANDゲートの入力端子数が3,4,5…と増えた場合も同様です。ANDゲートのすべての入力端子の値が1の時だけ、出力端子の値が1になります。

| 入力 | 出力 | ||

|---|---|---|---|

| A | B | C | Z |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |