フリップフロップには、エッジトリガ型とマスタースレーブ型の種類があります。

エッジトリガ型が入力信号をクロックのエッジでフリップフロップの内部に取り込むのに対して、マスタースレーブ型は入力信号をクロックの0と1の期間で段階的に取り込みます。

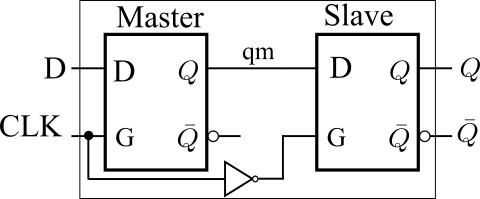

図1はマスタースレーブ型Dフリップフロップの例です。内部にマスターのDラッチとスレーブのDラッチを持ちます。前段のマスターDラッチは、CLKが1の期間にDを透過的にQから出力し、CLKが0の期間はCLKが1から0に変化した時のQの保持します。後段のスレーブDラッチは、CLKが0の期間にDを透過的にQから出力し、CLKが1の期間はCLKが0から1に変化した時のQの保持します。このようにマスターとスレーブのDラッチが交互にデータの取り込みと保持の動作をすることで、CLKのサイクル単位でQ出力を安定させることができます。

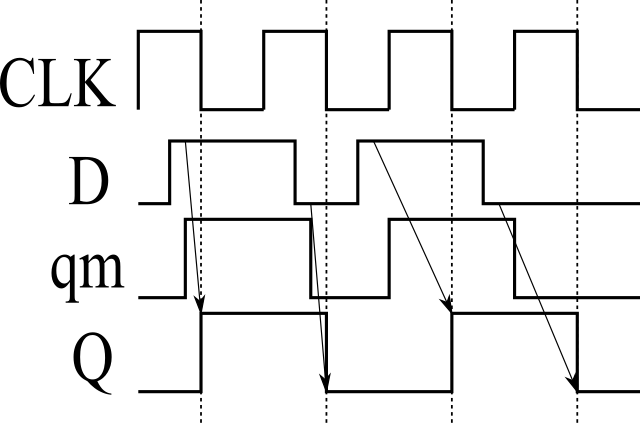

図2は図1の動作を表すタイミングチャートです。スレーブ側のDラッチには反転したCLKが入力されているので、Q出力はCLKの立ち下がりタイミングで変化します。

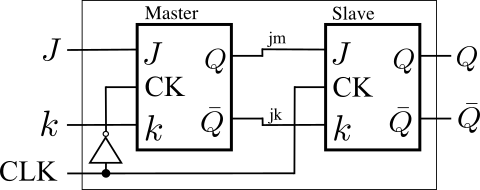

図3はマスタースレーブ型JKフリップフロップの内部概念図です。内部は2つの(エッジトリガタイプではない)JKフリップフロップで構成されます。実際にはマスター側のQ出力を決定するための信号として、スレーブ側の出力信号がマスター側に入力されますが、図3では省略しています。マスター側は、CLK=0の期間に外部信号のJとKを内部に取り込み、CLK=1の期間はその値を保持します。スレーブ側は、CLK=1の期間にマスター側の出力をJとKとして取り込み、CLK=0の期間はその値を保持します。

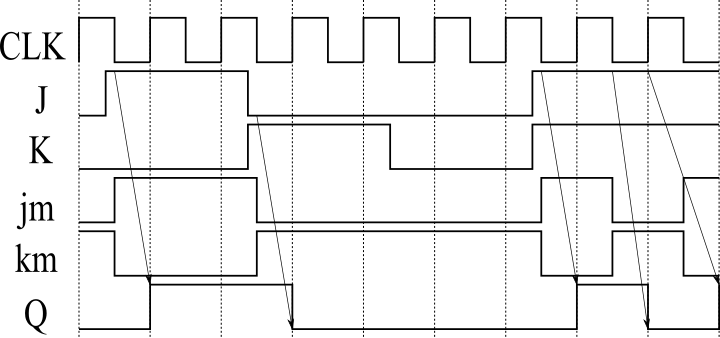

図4は図3の動作を表すタイミングチャートです。マスター側に反転したCLKが入力され、スレーブ側にはCLKがそのまま入力されているので、Q出力はCLKの立ち上がりタイミングで変化します。JKフリップフロップをこのようなマスタースレーブ型の構成にすることで、CLK=1の期間に外部入力のJ=1, K=1が連続したとしても出力Qが発振することなくCLKに同期して正常に動作します。