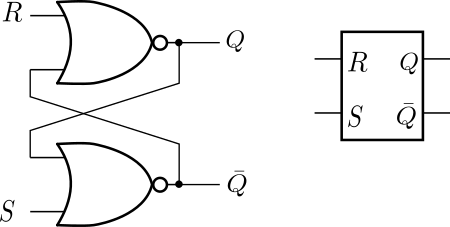

RSフリップフロップは、論理回路が値を保持する仕組みを説明するために良く用いられるフリップフロップです。図1は回路図でRSフロップフロップを表すシンボルです。RSフリップフロップの内部は、2つの2入力NORゲートで構成されます。入力端子としてSとR、出力端子として\(Q\)と\(\overline{Q}\)を持ちます。\(\overline{Q}\)は\(Q\)の反転値が出力されます。

RSフリップフロップの真理値表が表1です。S=1でQの値を1にセットします。また、R=1でQの値を0にリセットします。S=1かつR=1の状態は禁止されています。

| 入力 | 出力 | ||

|---|---|---|---|

| S | R | \(Q\) | \(\overline{Q}\) |

| 0 | 0 | \(Q_{PREV}\) | \(\overline{Q_{PREV}}\) |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 禁止 | 禁止 |

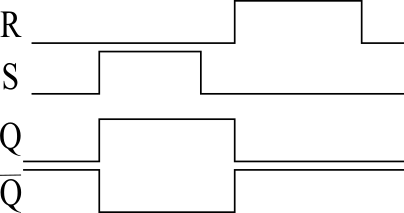

図2はRSフリップフロップの動作を表すタイミングチャートです。S=1かつR=0でQ=1になります。また、S=0かつR=1でQ=0になります。S=0かつR=0のときは、Qはそのままの状態を保持します。

真理値表とカルノー図からRSフリップフロップの論理式を作成する例はこちら