デコーダは、入力された数値に対応する出力信号をON/OFFする回路です。数値に応じたLEDの点灯や、DMMのような複数のメモリモジュールを選択するためのチップセレクト信号の生成などの用途で利用されます。

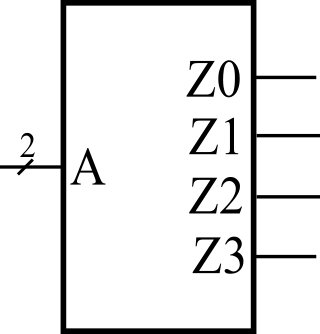

図1は、2ビットの入力信号の値に応じて4本の出力信号をON/OFFするデコーダのシンボルです。表1は、図1のデコーダの真理値表です。入力Aは2ビットで、下位ビットをA[0]で表し、上位ビットをA[1]で表します。入力信号A=0(\(00_{2}\))のときはZ0=1、A=1(\(01_{2}\))のときはZ1=1といったように、入力信号の数値に対応した出力ビットが1になります。デコーダの入力信号がNビットのとき、最大で\(2^{N}\)本の信号を出力します。

| 入力 | 出力 | ||||

|---|---|---|---|---|---|

| A[1] | A[0] | Z0 | Z1 | Z2 | Z3 |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

デコーダの論理式

出力Z0〜Z3について、表1から主加法標準形で論理式を作成します。各出力ビットが1になる組み合わせは1つしかないので、論理式の作成は簡単です。

$$Z0 = \overline{A[1]} \cdot \overline{A[0]}\ \ \ \ \ \text{(1)}$$ $$Z1 = \overline{A[1]} \cdot A[0]\ \ \ \ \ \text{(2)}$$ $$Z2 = A[1] \cdot \overline{A[0]}\ \ \ \ \ \text{(3)}$$ $$Z3 = A[1] \cdot A[0]\ \ \ \ \ \text{(4)}$$

HDL記述

2ビットのデコーダをVerilogで記述したのがリスト1です。式(1)〜(4)をほぼそのままコード化しています。複雑なデコーダはfunctionで関数化する場合もあります。

リスト1