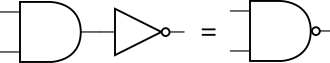

入力端子と出力端子の本数がそれぞれ1本の、最もシンプルな基本ゲートがNOTゲートです。NOTゲートは、入力端子に入力された値を反転して出力端子から出力します。入力値を反転して出力することから、インバータ(inverter)とも呼ばれます。NOTゲートは、図1のシンボル、または(1)の論理式で表されます。NOTゲートのシンボルは、他の基本ゲートと接続される時は、その基本ゲートの入出力端子に接した○として表されます(図2)。

$$Z = \overline{A} \ \ \ \ \ \text{(1)}$$

基本ゲートの機能は、真理値表(truth table)で表されます。真理値表は、入力端子に入力される値の取り得る組み合わせと、その組み合わせに応じて出力端子から出力される値の対応表です。表1は、NOTゲートの真理値表です。 入力端子にはAという端子名、出力端子にはZという端子名を付けています。入力端子が1本のNOTゲートの入力端子は、0または1のどちらかの値を取り得るので、組み合わせは\(2^1=2\)通りです。

真理値表の1行目は、列ごとのラベルを表します。表1の場合、1列目は入力端子Aの状態を表し、2列目は出力端子Zの状態を表します。表1の2行目を見ると、NOTゲートの入力端子Aに0が入力されると、出力端子Zから1が出力されることがわかります。また、3行目を見ると、入力端子Aに1が入力されると、出力端子Zから0が出力されることがわかります。このように、NOTゲートは入力端子Aから入力された値の反転値を出力端子Zから出力することがわかります。

| 入力 | 出力 |

|---|---|

| A | Z |

| 0 | 1 |

| 1 | 0 |

リスト1は、ハードウェア記述言語(HDL)のVerilogで記述したNOTゲートです。リスト1は、NOTゲートに対応させる形で機能をモジュール化していますが、実際のVerilog設計では信号を反転するためにNOTゲートをモジュール化して使用することは、特殊な場合を除いてほとんどありません。

リスト1

module not_mod (

input A,

output Z

);

assign Z = ~A;

endmodule