論理回路設計では、論理回路をある機能ごとにまとめてブロック化し、複数のブロックを組み合わせることで複雑な機能を持った論理回路を実現します。

複数のブロックを組み合わせる場合、それらのブロックは単一のクロックに同期して動作するように設計することが一般的です。同期式の論理回路では、クロック信号に同期してすべてのブロックの入出力信号が変化します。このようなブロックは、内部に組み合わせ回路と順序回路を持ちますが、信号が変化するタイミングによって、ムーア(Moore)・マシンとミーリー(Mealy)・マシンと呼ばれる2つの種類に分類されます。ムーア・マシンはムーア型、ミーリー・マシンはミーリー型と呼ばれることがあります。

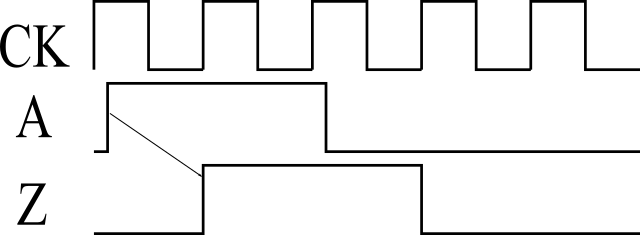

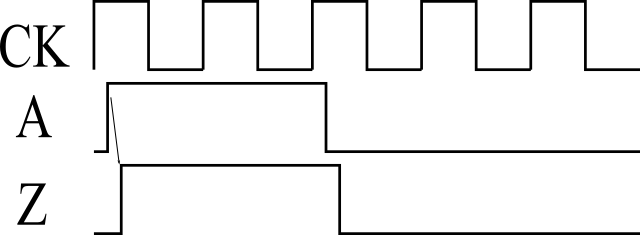

ムーア・マシンとミーリー・マシンの違いは、ブロックの入力信号の変化と出力信号の変化のタイミングです。図1は、ムーア・マシンとミーリー・マシンの論理回路ブロックの例です。どちらのブロックも、クロック信号CKに同期して動作します。

ムーア・マシンは、ブロックの出力信号にブロックの入力信号が直接関係しません。このため、出力信号の値は現在のフリップフロップの状態だけで決まります。一方、ミーリー・マシンは、ブロックの出力信号にブロックの入力信号が関係します。このため、出力信号の値は現在のフリップフロップの状態と入力信号の値の両方で決まります。

図2は、図1で入力信号Aが変化したときの出力信号Zの変化タイミングを示す例です。入力信号Aが変化したとき、ムーア・マシンの回路ブロックは、クロック信号CKの次のサイクルまで出力信号Zが変化することはありません。

一方、ミーリー・マシンの回路ブロックは、入力信号Aが変化したとき、その変化に応じて出力信号Zが直ちに変化する可能性があります(図3)。

ブロック間のインターフェース信号を設計する場合は、論理回路ブロックがムーア・マシンで設計されているか、ミーリー・マシンで設計されているかを注意する必要があります。

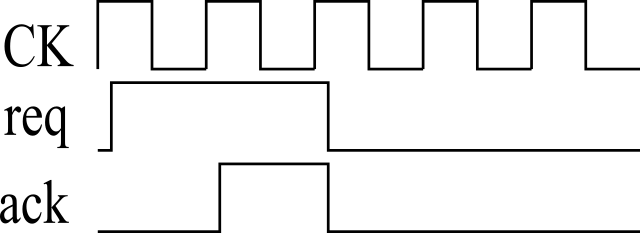

ブロック間のデータの受け渡しには、図4のようなリクエスト/アクノリッジ方式が良く用いられます。リクエスト/アクノリッジ方式は、前段ブロックのリクエスト信号(req)と後段ブロックのアクノリッジ信号(ack)が両方1になったクロックCKのサイクルで、ブロック間のデータの受け渡しが完了します。

図5は、ブロック間のリクエスト/アクノリッジの処理に問題のある回路例です。図5の送信ブロックと受信ブロックはどちらもミーリー・マシンです。送信ブロックのreq出力信号は、受信ブロックから入力されるack信号が0のときに1になります。一方、受信ブロックのack出力信号は、送信ブロックから入力されるのreq信号が1のときに1になります。このような2つのミーリー・マシンのブロックを接続すると、ブロック間でreq信号とack信号に組み合わせ回路のループが発生することになり、論理回路として正常に動作しません。