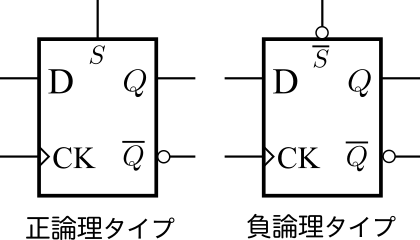

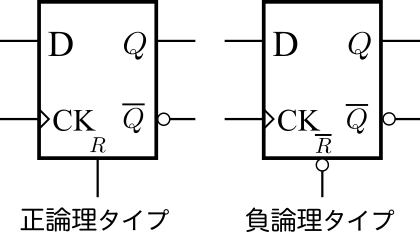

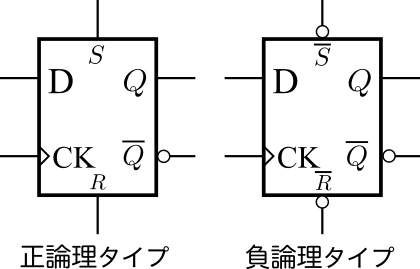

フリップフロップやラッチは内部に0または1の値を保存しますが、電源投入時などの初期状態でどちらの値になるかは不確定です。計算結果を保存するためのフリップフロップやラッチであれば、実際に計算を行うまで値が不確定でも問題ありませんが、LEDのON/OFFを制御するようなフリッププロップやラッチは、初期状態が不確定だと動作が不安定になり問題がります。このため、初期状態を確定する必要があるフリップフロップやラッチは専用端子を持ちます。図1は初期状態を1に設定する専用端子を持つフリップフロップの例、図2は初期状態を0に設定する専用端子を持つフリップフロップの例、図3は両方の専用端子を持つフリップフロップの例です。初期状態を1にする端子はプリセット端子、初期状態を0にする端子はリセット端子と呼ばれますが、名称や極性には各種のバリエーションがあります(表1)。また、0や1に初期化するためにクロック入力が必要かどうかで、同期タイプと非同期タイプに別れます(表2)。

同期タイプの場合、クロックが入力されていないとセットやリセットが行われません。非同期タイプの場合、クロックが入力されているかどうかに関係なく、セット端子やリセット端子の制御だけで初期化が行われます。

| 初期値 | 意味 | 端子形 | 極性 |

|---|---|---|---|

| 0 | クリア | \(C, CLR\) | 正 |

| 0 | クリア | \(\overline{C},\overline{CLR}\) | 負 |

| 0 | リセット | \(R,RES\) | 正 |

| 0 | リセット | \(\overline{R},\overline{RES}\) | 正 |

| 1 | セット | \(S, SET\) | 正 |

| 1 | セット | \(\overline{S},\overline{SET}\) | 正 |

| 1 | プリセット | \(PRE\) | 正 |

| 1 | プリセット | \(\overline{PRE}\) | 正 |

| タイプ | 意味 |

|---|---|

| 同期 |

クロックに同期して初期化を実行 クロック入力が必要 |

| 非同期 |

クロックに同期しない クロック入力は不要 |

初期化されていないフリップフロップは、HDLシミュレーションでは不定扱いになります。不定とは”0なのか1なのかわからない”状態を表すシミュレーション特有の状態です。

現実世界の初期化されていないフリップフロップは、0と1のどちらの値になるかはっきりしない場合であったとしても、0と1以外の値になることはありません。

FPGAで論理設計を行う場合は、フリップフロップの初期値を指定できる場合があります。