タイミングチャートは、論理回路の信号変化のタイミングや信号間の関係を表す図です。組み合わせ回路と順序回路について、簡単なタイミングチャートの例を紹介します。

組み合わせ回路

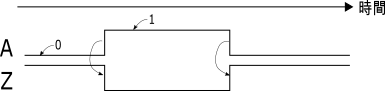

図2は、NOTゲート(図1)のタイミングチャートです。タイミングチャートは、左側から右側に時間が進みます。図2のタイミングチャートは、「入力端子Aが0→1→0と変化した時、出力端子Zは1→0→1と変化する」という動作を表しています。タイミングチャートの各信号は、2段階のレベルを持ち、低いレベル(Lレベル)が0、高いレベル(Hレベル)が1の状態を表します。一般的に、タイミングチャートの対象となる論理回路の入力信号を上側に、入力信号の変化によって値が変化する信号を下側に書きます。

タイミングチャートは、信号の表現にいくつかの種類があり、タイミングチャートを利用する目的に合った抽象度の表現が選ばれます。

図2は、次のような論理回路の電気特性や遅延時間の表現を省略したタイミングチャートです。

- 論理ゲートの入力端子から出力端子までの信号伝搬の遅延時間

- 論理ゲートの出力端子の状態遷移(0→1, 1→0)に必要な時間

- 温度・電圧による論理ゲートの遅延時間の変化

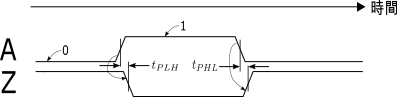

論理回路の機能検討を行う場面では、図2のような省略したタイミングチャートが良く用いられます。一方、図3は、論理回路の遅延時間を一部考慮したタイミングチャートです。図3は、図2と次の点が異なります。

- AとZの変化にわずかに時間がかかる(信号の変化が直角ではなく、斜めの線で表されている)

- Aが変化した時、その反転値がZに出力されるまで、わずかに時間がかかる(\(t_{PLH}\),\(t_{PHL}\))

図3の\(t_{PLH}\),\(t_{PHL}\)は、信号の遷移時間を意味します。表1のように、一般的に論理回路の信号遷移時間は、0→1の時と0→1の時で異なります。図3のような信号遅延を考慮したタイミングチャートは、FPGAなどのICデバイスで入出力特性を規定する場合などに用いられます。

| 記号 | 意味 |

| \(t_{PLH}\) | Aが1から0に変化した時、Zが0から1に変化するために必要な時間 |

| \(t_{PHL}\) | Aが0から1に変化した時、Zが1から0に変化するために必要な時間 |

順序回路

フリップフロップやラッチを用いた順序回路は、クロックと呼ばれる0と1を周期的に繰り返す信号を基準に動作します。このため、順序回路のタイミングチャートはクロック信号を基準に考えます。

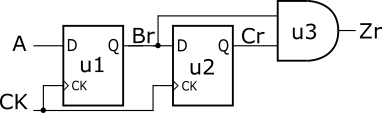

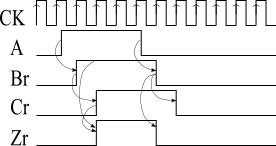

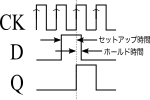

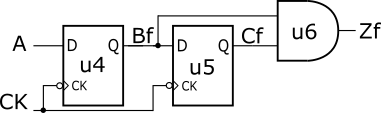

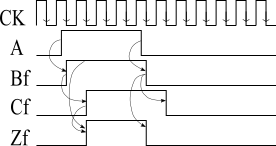

図4は、Dフリップフロップを用いた順序回路です。図4の入出力と内部の信号を表したタイミングチャートが図5です。クロック信号CKの立ち上がりエッジに同期して処理が行われるので、タイミングチャートのCKの立ち上がり部分(0→1に変化する部分)に矢印が書かれています。この回路は、u1とu2のDフリップフロップのQ出力が両方共に1になったクロック周期でZr=1になります。図5のタイミングチャートも、組み合わせ回路のタイミングチャート図2と同様に、論理回路の遅延時間に関するパラメータが省略されています。例えば、実際のDフリップフロップは、基準となるクロック信号のエッジの前後一定期間は、入力信号Dが変化してはいけないという決まりがあります(図6)。図5は、このようなタイミング制約は省略されたタイミングチャートです。

図4のDフリップフロップをクロックの立ち下がりエッジに同期して動作するタイプに置き換えた回路とタイミングチャートが、図7と図8です。図7は、Dフリップフロップが立ち下がりエッジに同期して動作する以外は、図4と同じ回路です。