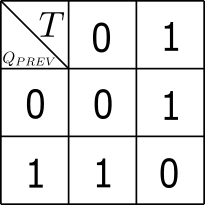

Tフリップフロップの真理値表(表1)から、等価な論理式を求めます。表1の\(Q_{PREV}\)は、現在のTフリップフロップの値を表します。また、\(Q\)はTと\(Q_{PREV}\)の値から決定される次の値を表します。Tフリップフロップはエッジトリガではないと仮定します。

真理値表とカルノー図から論理式を作成する題材としてTフリップフロップを取り上げていますが、実際の論理回路設計で基本ゲートの組み合わせによってTフリップフロップを実現することはまずありません。

| 入力 | 出力 | |

|---|---|---|

| T | \(Q_{PREV}\) | Q |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

表1から主加法標準形で直接論理式を作成することもできますが、論理式を最適化できる可能性を検討するために、まずカルノー図を作成します。表1からQについて作成したカルノー図が図1です。セル中の値がQを表します。

カルノー図から最適化できそうな部分は無いので、主加法標準形で論理式を求めます。

$$Q = T \cdot \overline{Q_{PREV}} + \overline{T} \cdot Q_{PREV} \ \ \ \ \ \text{(1)}$$

Verilogシミュレーションで動作を確認

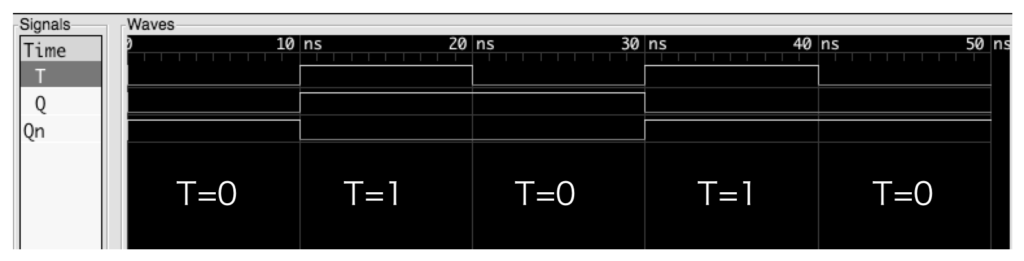

(1)の論理式を記述したTフリップフロップのモジュールを作成し、Tの値を10ナノ秒単位で切り替えてQの値を確認します。シミュレーションではQの初期値を0としています。

`timescale 1ns/1ns

// Tフリップフロップのモジュール

module t_ff (

input T,

output reg Q,

output Qn

);

assign Qn = ~Q; // Qの初期値は0

initial Q = 0;

always @*

Q = (T & ~Q) | (~T & Q); // 論理式

endmodule

module top;

reg T;

wire Q,Qn;

t_ff u_t_ff(.T(T),.Q(Q),.Qn(Qn)); // Tフリップフロップのインスタンス

initial begin

$dumpvars; //波形出力

T = 0; // 10nSごとにTを切り替える

#10;

T = 1;

#10;

T = 0;

#10;

T = 1;

#10;

T = 0;

#10;

$finish;

end

endmodule結果確認

シミュレーションで出力される波形をを確認すると、確かにT=1でQが反転しています。

module t_ffは論理式の動作を確認することを目的としたシミュレーション用であり、実際のFPGAやASIC向けの論理設計でこのような記述のTフロップフロップを実装することはまずありません。