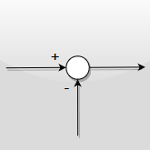

1次遅れ要素とは

ブロック線図の要素の一つです。入力に対する出力の遅れをモデル化したものです。伝達関数の最高時数が1であることから、1次遅れ要素と呼ばれます。

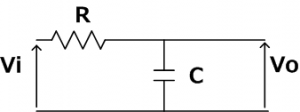

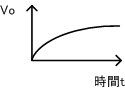

電気系では積分回路が1次遅れ要素です。コンデンサの両端電圧は、電源投入後、一定電圧に収束するまでに時間がかかります。このような遅れは、1次遅れ要素で表されます。

1次遅れ要素の伝達関数

1次遅れ要素の伝達関数は次のように表されます。

$$ G(s) = \frac{K}{Ts + 1} $$

ここで

- K:ゲイン(または比例ゲイン)

- T:時定数

Tが小さいほど、入力に対して出力が速く応答します。

RC積分回路の場合

伝達関数の時定数Tは、回路の抵抗RとコンデンサCで決まります。

$$ G(s) = \frac{Vo(s)}{Vi(s)} = \frac{1}{RCs + 1} $$

$$ K=1, T=RC $$